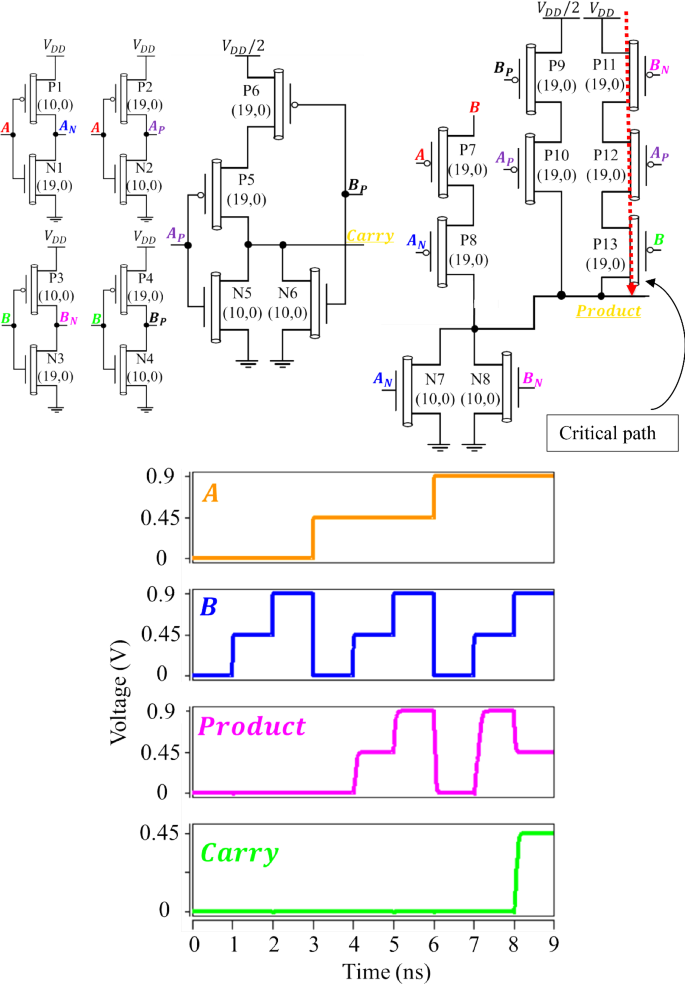

Efficient MVL Circuit Design with Use of p-CNTFETs and n-CNTFETs

Por um escritor misterioso

Descrição

Efficient MVL Circuit Design with Use of p-CNTFETs and n-CNTFETs

DG-CNTFET simulation. (a) Simulation setup. (b) Simulated n-branch

Design and evaluation of energy-efficient carbon nanotube FET-based quaternary minimum and maximum circuits

A universal method for designing low‐power carbon nanotube FET‐based multiple‐valued logic circuits - Moaiyeri - 2013 - IET Computers & Digital Techniques - Wiley Online Library

Design and evaluation of energy-efficient carbon nanotube FET-based quaternary minimum and maximum circuits - ScienceDirect

A universal method for designing low‐power carbon nanotube FET‐based multiple‐valued logic circuits - Moaiyeri - 2013 - IET Computers & Digital Techniques - Wiley Online Library

Design of Area Optimised, Energy Efficient Quaternary Circuits Using CNTFETs

Full article: A novel, efficient CNTFET Galois design as a basic ternary-valued logic field

Design and evaluation of energy-efficient carbon nanotube FET-based quaternary minimum and maximum circuits

Fault Tolerance in Carbon Nanotube Transistors Based Multi Valued Logic

A High-Performance and Energy-Efficient Ternary Multiplier Using CNTFETs

PDF) Carbon Nanotube Field Effect Transistor (CNTFET) and Resistive Random Access Memory (RRAM) Based Ternary Combinational Logic Circuits

Full article: Design of CNTFET-based 2-bit ternary ALU for nanoelectronics

Design and evaluation of energy-efficient carbon nanotube FET-based quaternary minimum and maximum circuits - ScienceDirect

PDF) Energy-Efficient Ternary Multipliers Using CNT Transistors

de

por adulto (o preço varia de acordo com o tamanho do grupo)